1G/10G/40G/100G UDPIP Core

Description:

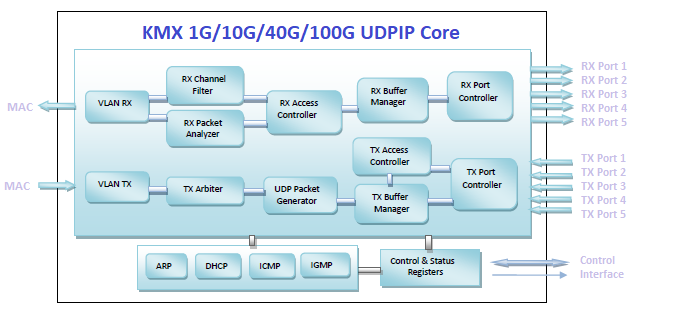

- High performance, ultra-low latency, great reliability and up to physical link speeds, the 1G/10G/40G/100G UDP/IP full protocol hardware stack cores can be used in both FPGA-based systems and ASIC designs.

- The cores support ARP protocol, and maintain ARP lookup table.

- The cores implement ICMP ping reply for checking network connectivity.

- DHCP client module is included for acquiring IP address from DHCP servers.

- The cores support V3 IGMP membership Query/Join/Leave messaging and UDP multicast traffic.

- 801.1Q tagging is supported for Virtual LAN operations.

- IP/UDP checksum generation and validation are implemented.

- Configurable UDP port filtering, IP address filtering are implemented.

- The cores support Jumbo packets of sizes up to 9KB in both RX and TX.

- Connecting to MAC module via AXI4-Stream bus, the cores are easy to integrate with Xilinx MAC cores, KMX MAC cores as well as other vendor MAC cores.

- Connecting to user logic through Control Interface of AXI4-Lite bus, five RX Ports of AXI4-Stream buses, five TX Ports of AXI4-Stream buses. The cores are easy to fit in user designs.

- 32 RX channels and 32 TX channels are implemented. Each of RX channels can be configured to associate with any of five RX Ports. Each of TX channels can be used to send packets on five TX Ports.

- Master access to external MDIO devices via AXI4-Lite bus is implemented.

- IP raw packets are supported for customer requirements, such as reliable communications.

- IP Fragmentation and TCP protocol harddware stack core are available on demand.

- High-configurable UDP/IP cores with well-designed register sets for easy and efficient network operations.

- Effectively handling burst traffic in RX and TX, the cores gracefully deal with internal resource exhaustion and invalid incoming packets.

- The cores support separate clock domains for packet processing and control interface to easily fit into different applications.

- KMX can customize the cores to meet customer requirements.

Deliverables

KMX 1G/10G/40G/100G UDPIP core in netlist format included, the delivery package contains everything required for successful integration, including VHDL source code of reference design and testbench, build script, constrain files, related documents.

Demonstration

Download the product datasheet documents:

©2016 KMX Embedded Core