1G/10G/40G/100G AN and LT Core

Description:

- KMX AN and LT core consists of anto-negotiation module and link-training module.

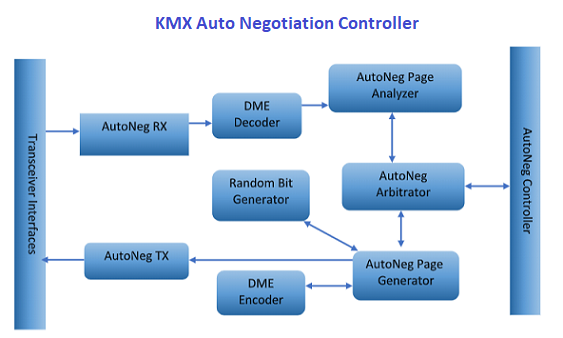

- The Auto-Negotiation module conforms to clause 73 in 802.3ap-2007. It consists of sub-modules of AutoNeg RX, AutoNeg TX, AutoNeg Page Generator, AutoNeg Arbitrator, AutoNeg Page Analyzer, DME Decoder and AutoNeg Control which are indicated in the above figure and described in details in the following:

- AutoNeg RX module reads 64 bit data from the transceiver RX interface, after RX lane 0 is locked, and reverses its bit order, pass it to DME Decoder.

- AutoNeg TX transmits the encoded negotiation page to the transceiver TX interface.

- AutoNeg Page Generator generates auto-negotiation page based on the information from AutoNeg Arbitrator and passes the pages to DME Encoder.

- AutoNeg Arbitrator implements the auto-negotiation arbitration defined in IEEE802.3ap-2007.

- AutoNeg Page Analyzer tracks the received negotiation pages, handles INITIALIZE, PRESET, ACK and NEXT pages defined in IEEE802.3ap-2007. It passes the page information to AutoNeg Arbitrator.

- DME Decoder decodes the received data for auto-negotiation pages and passes them to AutoNeg Page Analyzer.

- AutoNeg Control connects to user logic and work with AutoNeg Arbitrator to control the Auto-Negotiation process. It determines when to start auto-negotiation and when to end it.

Description:

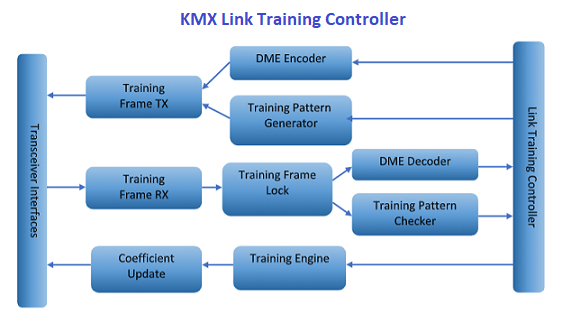

- The Link-training module conforms to clause 72 in 802.3ap-2007. It consists of sub-modules of Training Frame RX, Training Frame Lock, DME Decoder, DME Encoder, Training Pattern Checker, Training Pattern Generator, Training Frame TX, Training Engine and Coefficient Update which are indicated in the above figure and described in details in the following:

- Training Frame RX checks if the lane 0 RX is locked (the RX output is valid) and when it is locked, read the data from Transceiver Interface data port and reverse the order of 64 bit, pass the data to Training Frame Lock module.

- Training Frame Lock implements Training Frame Lock algorithm defined in 802.3ap-2007. When Training Frame is locked, pass the received data from GTH RX port to DME Decoder and Training Pattern Checker.

- DME Decoder decodes the received training frames for the control channel message when training frame lock is achieved.

- Training Pattern Checker checks the training pattern bit stream received from Link Partner and passes the results to Link Training module.

- DME Encoder generates control channel in DME format defined in 802.3ap-2007 and passes the encoded control channel bit stream to Training Frame TX.

- Training Pattern Generator generates the training pattern bit stream from polynomial x9 + x6 + 1 with seed configured by user logic and passes them to Training Frame TX.

- Training Frame TX generates training frames and writes them to Transceiver Interfaces.

- Training Engine implements the Training State defined in 802.3ap-2007.

- Coefficient Update configures the RX equalizer of Xilinx GTH with coefficient update value from Training Engine. This module is Xilinx FPGA dependent. It uses the DRP (Dynamic Reconfiguration Port) to update link coefficients to get better RX equalizer. The coefficient initial value is read from Transceiver Interfaces.

- Link Training controls Link Training process and determines when it starts and when it ends.

- KMX can customize the core to meet customer requirements.

Deliverables

KMX AN and LT core in netlist format included, the KMX delivery package contains everything required for successful integration, including VHDL source code of reference design and testbench, build script, constrain files and related documents.

Download the product datasheet document:

©2016 KMX Embedded Core