10G/40G/100G MAC and PCS Core

Description:

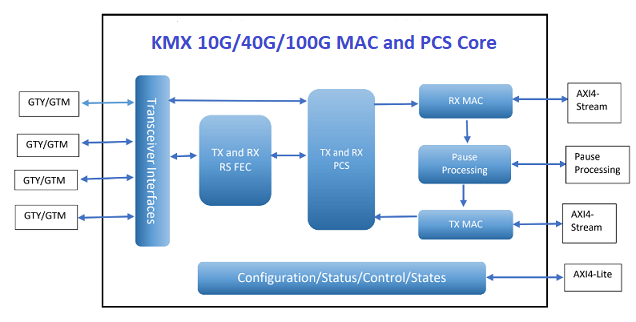

- KMX MAC and PCS core consists of MAC module and PCS module in 10G/40G/100G.

- The MAC module connects to user logic via AXI4-Stream interfece and to PCS core via XGMII/XLGMII/CGMII interfaces respectively.

- On TX path, the MAC core constructs packets by adding preamble/SFD and padding zero bytes for short packets to 64 bytes and on RX path, it removes preamble/SFD bytes.

- It generates 32 bits CRC and pads it to the packets on TX path and it checks CRC and removes it on RX path.

- The core implements Pause Frame processing for flow control.

- It implements Deficit Idle Count algorithm and VLAN tagged frame defined in IEEE 802.1Q.

- The core implements MAC loopback for debug purpose at the interfaces of XGMII/XLGMII/CGMII.

- The PCS module connects to the MAC interface and to the transceiver interface.

- The core implements PCS RS FEC with independent error bit detection and error bit correction.

- The PCS link fault signaling protocol defined in IEEE803.3ba is supported in the core.

- The standard 64/66B encoding/decoding algorithm is included.

- The PCS gearbox implementation is included on TX and RX.

- The PCS module implements scrambling/descrambling on TX and RX.

- The core implements multilane distribution (MLD) acrossing Virtual Lanes.

- It implements periodic insertion of Alignment Marker (AM) on TX and deletion of AM on RX for 40G and 100G.

- The core implements 66-bit block synchronization and Alignment Marker Lock algorithm in RX as specified in IEEE803.3ba.

- It implements skew compensation logic in order to realign all the virtual lanes and reassemble an aggregate stream (with all 64b/66b blocks in the correct order).

- For 40G and 100G, the virtual lane reordering is included.

- It supports BIP-8 calculation and insertion on each TX Virtual Lane and checking and deletion per RX Virtual Lane.

- The core implements internal loopback at the transceiver interface for debug purpose, which redirects traffic received from TX path to RX path and no data is forwarded to the transceiver TX interface.

- It implements Bit Error Rate (BER) for monitoring excessive error ratio.

- The core implements configuration, control, status and statistical information collection in MAC module and PCS module.

Deliverables

KMX 10G/40G/100G MAC and PCS core in netlist format included, the delivery package contains everything required for successful integration, including VHDL source code of reference design and testbench, build script, constrain files, related documents.

Demonstration

Download the product datasheet documents:

©2016 KMX Embedded Core